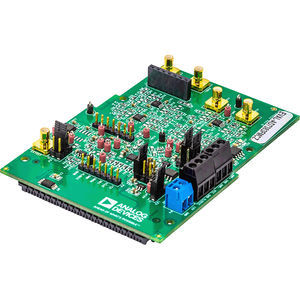

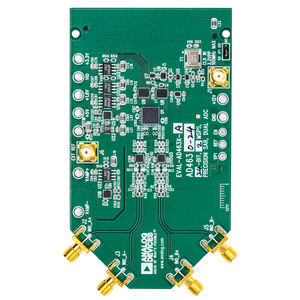

Rectificador de corriente industrial AD9082 series

Añadir a mis favoritos

Añadir al comparador

Características

- Otras características

- industrial

- Potencia

11,45 W

- Tensión

1,48 V

- Corriente primaria

Máx.: 37,75 mA

Mín.: 6,43 mA

Descripción

Diseño de plataforma común flexible y reconfigurable

Opciones de 4 DAC y 2 ADC (4D2A) y 2D2A

Admite banda única, doble y cuádruple

Las rutas de datos y los bloques DSP son totalmente derivables

Relaciones de frecuencia de muestreo de DAC a ADC de 1, 2, 3 y 4

PLL en chip con sincronización multichip

Opción de entrada RFCLK externa para el PLL fuera del chip

Velocidad de muestreo máxima del DAC de hasta 12 GSPS

Velocidad máxima de datos de hasta 12 GSPS mediante JESD204C

Ancho de banda analógico utilizable hasta 8 GHz

Velocidad máxima de muestreo del ADC de hasta 6 GSPS

Velocidad máxima de datos de hasta 6 GSPS utilizando JESD204C

Ancho de banda analógico utilizable hasta 8 GHz

Rendimiento del ADC ac a 6 GSPS, entrada a 2,7 GHz, -1 dBFS

Tensión de entrada a escala completa: 1,475 V p-p

Densidad de ruido: -147,5 dBFS/Hz

Figura de ruido: 25,3 dB

HD2: -72 dBFS

HD3 -68 dBFS

El peor de los casos (excluyendo HD2 y HD3): -78 dBFS

Rendimiento del DAC ac a 12 GSPS, salida a 2,6 GHz

Rango de corriente de salida a escala completa: 6.43 mA a 37,75 mA

IMD3 de dos tonos (-6 dBFS por tono): -72 dBc

NSD, un solo tono: -160 dBc/Hz

SFDR, un solo tono: 75 dBc

Funciones digitales versátiles

Filtros de interpolación y decimación seleccionables

DDC y DUC configurables

8 DUCs complejos finos y 4 DUCs complejos gruesos

8 DDC complejos finos y 4 DUC complejos gruesos

NCO de 48 bits por DUC o DDC

Opción de puentear DUC/DDC finos y gruesos

Filtro PFIR programable de 192 tomas para la ecualización de la recepción

Admite 4 configuraciones de perfil diferentes cargadas a través de GPIO

Retardo programable por ruta de datos

Soporte de AGC de recepción

Detección rápida con baja latencia para un control rápido del AGC

Monitorización de la señal para el control lento del AGC

Pines de soporte de AGC dedicados

Soporte de DPD de transmisión

Control de ganancia de canal DUC fino y ajuste de retardo

Ajuste de retardo DDC grueso para la ruta de observación DPD

Funciones auxiliares

Salto rápido de frecuencia

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de ADIBúsquedas asociadas

- Módulo conversor DC DC

- Convertidor DC/AC

- Rectificador de corriente Linear Technology

- Módulo conversor DC DC conmutado

- Convertidor DC/AC de potencia

- Ondulador DC/AC para aplicaciones industriales

- Ondulador DC/AC de corriente

- Convertidor DC/DC de potencia

- Convertidor DC/AC DC

- Convertidor DC/AC IEC

- Convertidor DC/AC online

- Módulo conversor DC DC ajustable

- Rectificador de corriente compacto

- Ondulador DC/AC RoHS

- Convertidor DC/DC programable

- Convertidor DC/DC regulador

- Ondulador DC/AC de alta velocidad

- Convertidor DC/DC con tecnología de inverter

- Convertidor DC/AC con salidas de tensión

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.