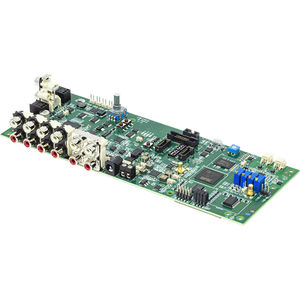

Microcontrolador 32 bits ADSP-21566 seriespara aplicaciones automovilísticasde uso generalanalógico

Añadir a mis favoritos

Añadir al comparador

Características

- Tipo

- 32 bits

- Aplicaciones

- de uso general, para aplicaciones automovilísticas

- Otras características

- analógico

Descripción

Infraestructura del núcleo SHARC

Frecuencia de reloj del núcleo de 400 MHz (máx.)

La memoria SRAM de nivel 1 (L1) en el chip (con paridad) aumenta el rendimiento de baja latencia

Soporte de coma flotante de 32, 40 y 64 bits

Punto fijo de 32 bits

Direccionamiento de bytes, palabras cortas, palabras largas

Memoria

256 KB de SRAM de nivel 2 (L2) en el chip con protección ECC: elimina la necesidad de memoria externa en muchos casos de uso

Una interfaz de nivel 3 (L3) optimizada para un bajo consumo del sistema, que proporciona una interfaz de 16 bits para dispositivos SDRAM DDR3 (compatible con dispositivos DDR3L de 1,35 V)

Controlador de memoria DDR/DDR3L de 16 bits

1.Soporte de 35 V para DDR3L

Aceleradores de hardware avanzados

Motores de descarga FIR/IIR mejorados que funcionan a la frecuencia de reloj del núcleo para una mayor potencia de procesamiento

Motores de criptografía de seguridad con OTP

Potente sistema DMA

La innovadora interfaz de audio digital (DAI) incluye

8x interfaces Full SPORT con modos TDM e I2S

2x S/PDIF Rx/Tx, 8 pares ASRC

4x generadores de reloj de precisión

28 búferes

Otros periféricos de conectividad/interfaces:

2x Quad SPI, 1x Octal SPI

MLB de 3 pines

6x I2C,3x UARTs

2x puertos de enlace

10x Temporizador de propósito general, 1x Contador de propósito general

2 temporizadores de vigilancia

ADCs de mantenimiento de 4 canales de 12 bits

40 pines GPIO, 28 pines DAI

Sensor térmico

17mm x 17mm (0.8mm pitch) 400-ball CSP_BGA

Seguridad y protección

Aceleradores de hardware de cifrado

Arranque rápido y seguro con protección IP

Aceleradores FIR e IIR mejorados que funcionan hasta 1 GHz

Calificación AEC-Q100 para aplicaciones de automoción

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de ADIBúsquedas asociadas

- Conmutador unipolar

- Amplificador de señal

- Transceptor

- Amplificador de potencia

- Transceptor Ethernet

- Convertidor industrial

- Transceptor de datos

- Amplificador electrónico

- Amplificador digital

- Amplificador de instrumentación

- Amplificador DC

- Amplificador de tensión

- Convertidor de potencia

- Amplificador analógico

- Amplificador de bajo ruido

- Amplificador de corriente

- Módulo transceptor Gigabit Ethernet

- Amplificador ajustable

- Microcontrolador

- Amplificador de audio

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.