- Productos

- Catálogos

- News & Trends

- Ferias

Software de desarollo ET9 seriesde gestión y de configuración de redde FPGApara red EtherCAT

Añadir a mis favoritos

Añadir al comparador

Características

- Función

- de desarollo, de gestión y de configuración de red

- Aplicaciones

- de FPGA, para red EtherCAT

- Sistema operativo

- Windows

- Otras características

- maestro, esclavo

Descripción

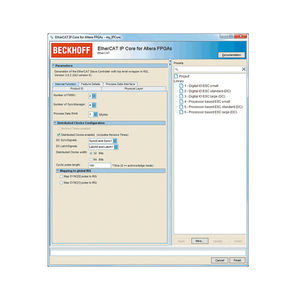

Los núcleos IP EtherCAT para FPGAs de Xilinx® e Intel® permiten implementar la función de comunicación esclava EtherCAT dentro de una FPGA. La funcionalidad EtherCAT -como el número de FMMUs y gestores SYNC, el tamaño de la DPRAM, etc.- puede configurarse para satisfacer los requisitos. Se ofrecen diferentes variantes de licencia.

Para la implementación maestra, los desarrolladores tienen a su disposición el código de muestra maestro, el código de pila esclavo EtherCAT y el configurador EtherCAT. Este último exporta un archivo de descripción de red (ENI - EtherCAT Network Information) a partir de los archivos de descripción de dispositivos (ESI - EtherCAT Slave Information) de los dispositivos conectados.

Las pruebas de conformidad requeridas para los dispositivos esclavos pueden realizarse internamente con la herramienta de prueba de conformidad EtherCAT (CTT). La herramienta avanzada de pruebas de conformidad FSoE (FSoE CTT) es adecuada para las pruebas de conformidad de los dispositivos esclavos para Safety over EtherCAT (FSoE).

---

Ferias

Este distribuidor estará presente en las siguientes ferias

Búsquedas asociadas

- Software resolutivo de automatización

- Software resolutivo de gestión

- Software resolutivo Windows

- Software de interfaz

- Software para la industria

- Software de programación

- Software resolutivo de red

- Software de creación

- Software de seguridad

- Software de autómata programable

- Software maestro

- Software de depuración

- Software de pilotaje CNC

- Software de FPGA

- Software EtherCAT

- Software esclavo

- Software para analizador de varios canales

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.