- Productos

- Tarjeta FPGA Mini PCIe

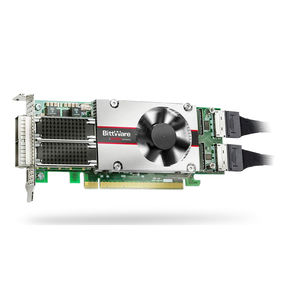

- BittWare

Tarjeta FPGA Mini PCIe IA-840Fcon procesador E/S

Añadir a mis favoritos

Añadir al comparador

Características

- Formato

- Mini PCIe

- Entrada/salida

- con procesador E/S

Descripción

Especificaciones del tablero

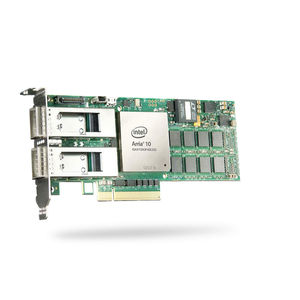

FPGA

Intel Agilex FPGA

AGF027 en un paquete R2581A

Grado de velocidad del núcleo -2: grado de velocidad de E/S -2

Contacte con BittWare para otras opciones de FPGA

Flash a bordo

Memoria Flash de 2Gbit para iniciar la FPGA

Memoria externa

2 ranuras DIMM de 288 pines, cada una de las cuales admite módulos SDRAM DDR4 de hasta 32 GB (hasta 64 GB en total)

Soporte diseñado para otros módulos DIMM como QDR SRAM. Contacte con BittWare para más detalles.

2 bancos de DDR4 integrados, hasta 32 GB cada uno

Interfaz del host...

x16 Interfaz Gen4 directo a FPGA, conectado a PCIe hard IP

Jaulas de QSFP-DD

3 jaulas QSFP-DD en el panel frontal conectadas directamente a la FPGA mediante 24 transceptores

El usuario puede programar el reloj de baja fluctuación que soporta 10/25/40/100GbE

Cada QSFP-DD puede ser cronometrado independientemente

Limpiador de jitter para el reloj recuperado de la red

MAC+FEC duro multitasa para 10/25/100GbE

MCIO

2 conectores de borde que admiten 4 complejos raíz PCIe Gen4 x4, 2 puntos finales Gen4 x8 o 1 complejo raíz o punto final Gen4 x16

Reloj externo

1 PPS y 10MHz ref clk entradas del panel frontal

USB micro

Acceso USB a BMC, USB-JTAG, USB-UART

Contralor de la Junta Directiva

Monitoreo de voltaje, corriente y temperatura

Secuenciación y restablecimiento de la energía

Mejoras en el campo

Configuración y control de la FPGA

Configuración del reloj

Las comunicaciones BMC-FPGA de bajo ancho de banda con enlace SPI

USB 2.0

El apoyo de PLDM

La tensión se anula

Catálogos

IA-840F

2 Páginas

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.