Digitalizador hasta 62,5 MS/s 64 canales12 bitsPCIe

Añadir a mis favoritos

Añadir al comparador

Características

- Velocidad

- hasta 62,5 MS/s

- Número de canales

- 64 canales

- Especificaciones

- 12 bits, PCIe, VME

Descripción

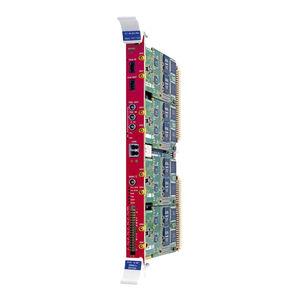

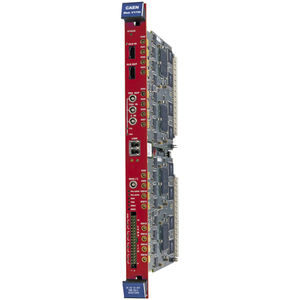

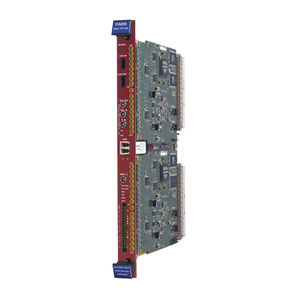

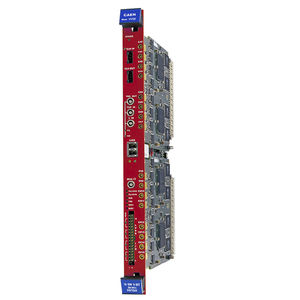

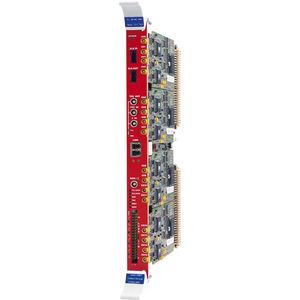

El V1740 es un módulo VME 6U de 1 unidad de ancho que aloja un digitalizador de forma de onda ADC Flash de 64 canales y 12 bits a 62,5 MS/s (65 MS/s utilizando reloj externo) y presenta una dinámica de entrada de 2 Vpp de terminación simple en dos conectores SMC ERNI. También hay disponibles versiones con un rango de escala completa de entrada de 10 Vpp (single ended) (V1740A/V1740C).

El ajuste del offset de CC (rango ±1 V / 5 V) mediante DAC de 16 bits programables (uno por cada grupo de 8 canales) permite un muestreo correcto de una entrada bipolar (Vin = ±1 V / 5 V) hasta una oscilación de entrada analógica totalmente positiva (Vin = 0 ÷ +2 V / 10 V) o negativa (Vin = 0 ÷ -2 V / 10 V) sin perder resolución dinámica.

El módulo dispone de entrada y salida de reloj en el panel frontal, así como de un PLL para la síntesis de reloj a partir de referencias internas/externas. El flujo de datos se escribe continuamente en un búfer de memoria circular. Cuando se produce el disparo, la FPGA escribe otras N muestras para el post-disparo y congela el buffer que puede ser leído tanto por VMEbus como por Optical Link. La adquisición puede continuar sin tiempo muerto en un nuevo buffer.

Cada canal dispone de un búfer multievento SRAM divisible en 1 ÷ 1024 búferes de tamaño programable. La lectura (por VMEbus o enlace óptico) de un búfer congelado es independiente de las operaciones de escritura en el búfer activo (almacenamiento de datos ADC). Dos tamaños de la memoria digital del canal están disponibles por opciones de pedido: 192 kS/ch (mod. V1740/V1740C) y 1,5 MS/ch (mod. V1740A/V1740B).

El V1740 admite sincronización multiplaca, lo que permite sincronizar todos los ADC a una fuente de reloj común y garantizar la alineación de los sellos de tiempo de disparo. Una vez sincronizados, todos los datos estarán alineados y serán coherentes en varias tarjetas V1740.

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de CAEN Spa* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.