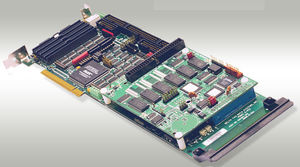

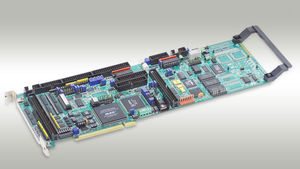

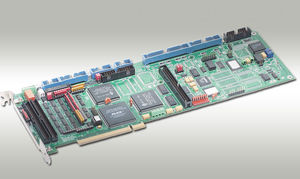

Tarjeta de control motor 8 ejes PMAC2A PC/104digitalPIDde alta eficacia

Añadir a mis favoritos

Añadir al comparador

Características

- Número de ejes

- 8 ejes

- Señal

- digital

- Tecnología

- PID

- Otras características

- de alta eficacia

Descripción

El PMAC2A PC/104 proporciona hasta 8 hachas de control en el factor de forma más pequeño que las ofertas del Tau del delta, capaces de salida filtrada de PWM, usando la CPU PMAC2.

CARACTERÍSTICAS DE HARDWARE

40 CPU del megaciclo DSP563xx (equivalente de OPT-5AF 80 megaciclo 560xx)

128K x 24 cero-espera-estados internos SRAM

memoria Flash 8 de 512K x para la copia de seguridad y el firmware del usuario

La última versión lanzada del firmware

Interfaz en serie RS-232

conjunto de circuitos del interfaz del eje de 4 canales, cada uno incluyendo:

salida analógica de 12-bit +/-10V

salida digital de la Pulso-y-dirección

Entradas A, B, C, canales del codificador de la cuadratura con los conductores diferenciados/de terminación única

4 banderas de la entrada, 2 banderas de la salida en los niveles de TTL

3 pares de la top-y-parte inferior de PWM (inseparados)

jefe de 50-pin IDC para el interfaz del amplificador/del codificador

jefe de 34-pin IDC para el interfaz de la bandera

Algoritmos servos de PID/notch/feedforward

garantía de un año a partir de la fecha del envío

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de Delta TauBúsquedas asociadas

- Servo-amplificador

- Servo-amplificador DC

- Servo-amplificador AC

- Servo-amplificador brushless

- Servo-amplificador digital

- Tarjeta de control motor multieje

- Tarjeta de control motor Ethernet

- Servo-variador de PWM

- Controlador de posición DC

- Tarjeta de control motor EtherCAT

- Tarjeta de control motor de servomotores

- Controlador de posición compacto

- Tarjeta de control motor paso a paso

- Tarjeta de control motor digital

- Tarjeta de control motor integrada

- Controlador de posición 1 eje

- Controlador de posición USB

- Tarjeta de control motor programable

- Controlador de posición 2 ejes

- Tarjeta de control motor 4 ejes

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.