- Robótica - Automatismos - Informática

- Informática industrial

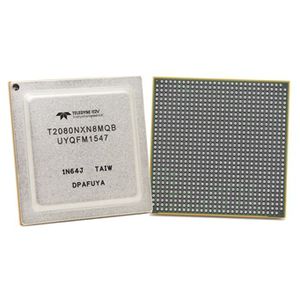

- Procesador 2 núcleos

- e2v scientific instruments

Procesador 2 núcleos PC8572E

Añadir a mis favoritos

Añadir al comparador

Características

- Número de núcleos

- 2 núcleos

Descripción

CARACTERÍSTICAS

- Doble núcleo integrado de e500, escalado hasta 1,5 GHz

- 6897 MIPS a 1500 MHz (Dhrystone estimado 2.1)

- Dirección física de 36 bits

- Soporte mejorado de depuración de hardware y software

- Unidad de coma flotante de doble precisión

- Unidad de gestión de memoria

- Caché L1/L2 integrado

- Caché L1: 32 KB de datos y 32 KB de caché de instrucciones con

Soporte de bloqueo de línea

- Caché L2 compartida: 1 MB con ECC

- L1 y L2 Coherencia de hardware

- L2 Configurable como SRAM, Cache y Transacciones de E/S puede

ser almacenado en regiones de caché L2

- Controlador de memoria DDR integrado con soporte completo de ECC,

Apoyando:

- Velocidad de reloj de 333 MHz (velocidad de datos de 667 MHz), 64 bits, 1,8 V

SSTL, DDR2 SDRAM

- Velocidad de reloj de 400 MHz (velocidad de datos de hasta 800 MHz), 64 bits,

1.5V SSTL, DDR3 SDRAM

- Plataforma de aceleración de aplicaciones

- TLU avanzado

- Motor de seguridad integrado que soporta DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RNG, Kasumi F8/F9 y ARC-4

Algoritmos de cifrado

- PME integrado (Expresión Regular)

- Motor de desinflado de paquetes

- Motor de seguridad integrado con XOR

- Cuatro controladores Ethernet de triple velocidad en el chip compatibles con

Redes Ethernet/IEEE 802.3 de 10 y 100 Mbps y 1 Gbps

con MII, RMII, GMII, SGMII, RGMII, RTBI y TBI Físico

Interfaces e IEEE 1588

- Aceleración de la suma de comprobación TCP/IP y QoS avanzada

Características

- Control de flujo sin pérdidas

- E/S de propósito general

- Serial RapidIO y PCI Express Interconexión de alta velocidad

Interfaces

- Tejido de conmutación de red en el chip (OCeaN)

- 133 MHz, 32-bit, 3.3V I/O, Bus Local con Memoria

Controlador

- Doble controlador DMA integrado

- Doble I

2

C y DUARTS

- Controlador de interrupción programable

- Puerto de acceso de prueba IEEE 1149.1 JTAG

- Voltaje del núcleo de 1.1V con E/S de 3.3V/2.5V/1.8V

- Paquete PBGA de 1023 patillas

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de e2v scientific instrumentsOtros productos de e2v scientific instruments

Semiconductors

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.