- Electricidad - Electrónica

- Componente Electrónico

- geb-enterprise

- Productos

- Catálogos

- News & Trends

- Ferias

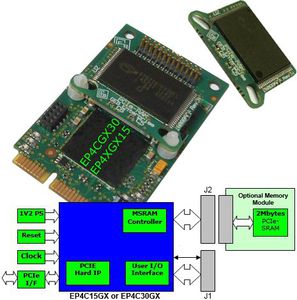

Puente PCI Express GPIO-BUS MS64-Windows| 141030-01A1

Añadir a mis favoritos

Añadir al comparador

Descripción

El IP de IOBUS es un amo asincrónico dinámicamente reconfigurable del autobús diseñado por empresa de GEB. Apoya interrupciones amplias, externas de 8/16/32 ómnibus de datos, estado latente fijo o ciclo variable del autobús del estado latente.

El IOBUS será el autobús usado para la comunicación entre un número principal (la tarjeta de Pcie) y sin especificar de esclavos. El autobús apoya hasta 32 bits de datos, dirección de hasta 8 pedacitos, viruta 2 selecta (CS#), leído permite (RD#), escribe la petición del estroboscópico (WR#), de interrupción (INT#) y una señal opcional de la espera (WAIT#).

En el lado interno del autobús, el IP de IOBUS es por completo obediente con la especificación de Altera Avalon, así que puede ser agregado fácilmente a cualquier diseño de Altera Qsys. En este lado, hay interfaz auxiliar de dos Avalon, primer se etiqueta MEM permite acces a los dispositivos externos. El segundo interfaz se etiqueta CSR, él ejecuta los registros de un espacio de configuración que se deben utilizar a programar las sincronizaciones. El CSR permite la programación de la disposición (ts), anchura de pulso (tpw), tiempo de asimiento (th) selectivamente para leído y escribe ciclos y también el usuario puede también permitir la petición de interrupción y las señales de la espera y su polaridad.

---

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.