Software de gestión Xpedition Substrate Integratorde visualizaciónde diseñode planificación

Añadir a mis favoritos

Añadir al comparador

¿Quiere comprar directamente?

Visite nuestra Shop.

Características

- Función

- de gestión, de visualización, de diseño, de planificación, de optimización, de verificación, de conectividad, de desarrollo de prototipos

- Aplicaciones

- de proceso

- Tipo

- 3D

Descripción

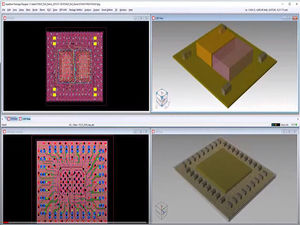

Planificación de la conectividad de paquetes de CI 2,5/3D heterogéneos y homogéneos, creación de prototipos de ensamblaje y cooptimización de tecnología de sistemas.

2.planificación y creación de prototipos de paquetes de CI 5/3D

La creación temprana de prototipos y la exploración permiten a los ingenieros evaluar diferentes escenarios de integración de ASIC/chiplet, intercalador, paquete y PCB con el fin de cumplir los objetivos generales de PPA, tamaño del dispositivo, ruteabilidad y coste antes de la implementación física detallada.

Características principales de Substrate Integrator

Importación de esquemas completos o parciales

La conectividad lógica del ensamblaje del paquete de CI puede construirse utilizando esquemas gráficos completos o parciales, lo que resulta útil para diseños con un elevado número de dispositivos, como los módulos SiP, y/o la reutilización/reorientación de diseños anteriores.

Gestión de la conectividad de paquetes a nivel de sistema

Gestión de la conectividad del sistema, visualización y verificación lógica a nivel de sistema de diseños de encapsulados de CI con múltiples componentes, sustratos y componentes.

Agregación de troqueles, chips y sustratos

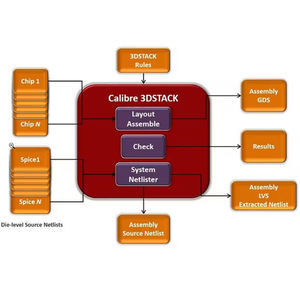

Xpedition Substrate Integrator integra matrices, chiplets e interpositores de diferentes nodos de proceso y proveedores. Admite varios formatos, como LEF/DEF, GDS, AIF y CSV/TXT. Los modelos jerárquicos de matrices virtuales admiten cambios ECO bidireccionales de objetos en proceso de diseño/optimización.

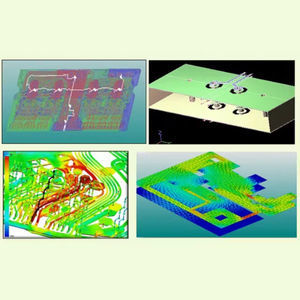

Cooptimización de sustratos cruzados Silicon-package-PCB

La planificación entre sustratos y la cooptimización mejoran enormemente la previsibilidad durante la implementación, ya que detectan y solucionan los problemas antes de que se conviertan en sorpresas de última hora. Una perspectiva de sistema con visibilidad entre sustratos mejora la comunicación y la coordinación mediante una respuesta inmediata a las decisiones que suelen tomarse en cada sustrato.

---

Catálogos

Xpedition Substrate Integrator

4 Páginas

Búsquedas asociadas

- Software resolutivo de automatización

- Software resolutivo de gestión

- Software resolutivo de proceso

- Software resolutivo Windows

- Software resolutivo de mando

- Software de CAD

- Software resolutivo en tiempo real

- Software en línea

- Software resolutivo de diseño

- Software de interfaz

- Software para la industria

- Software de medición

- Software de calidad

- Software de simulación

- Software resolutivo de visualización

- Software automatizado

- Software resolutivo de red

- Software de ingeniería

- Software de máquina

- Software de GED

* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.